In our new series, Common Electronics Design Pitfalls, we’ll explore mistakes that can undermine circuit performance, even for experienced engineers. Throughout this series, we’ll cover both common and less obvious design errors across topics like ADC/DAC challenges, digital circuit design, power supply issues, PCB layout mistakes, high-speed signal integrity, and more, providing practical solutions to avoid or correct them.

In this first part: Top Op-Amp Mistakes to Avoid—we focus on operational amplifiers, one of the most versatile yet commonly misused components in electronics. From stability issues to incorrect biasing, we’ll break down critical pitfalls and best practices to ensure reliable performance. Let’s dive in and refine our designs for better performance and reliability.

1. Fundamental Op-Amp Design Mistakes to Avoid

Not Providing a DC Path for Input Bias Current

One common problem when designing a circuit with op-amps is forgetting to provide a DC path for the input bias current. We will explain this with two common examples, an integrator circuit, and an AC-coupled amplifier.

Integrator circuit: working principle

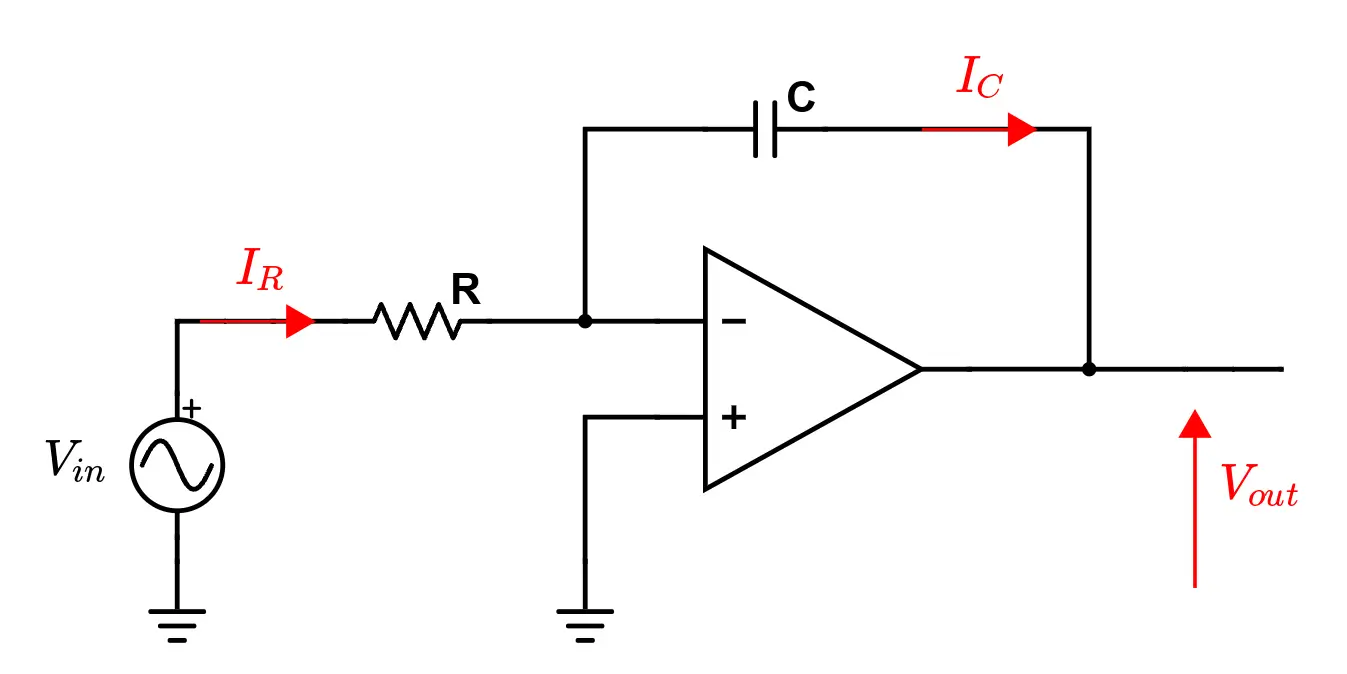

Figure 1 shows a basic integrator circuit—an operational amplifier in an inverting configuration with a feedback capacitor:

Let’s analyze how this circuit works by deriving its key equations. Because the circuit has closed-loop feedback, the voltage at the op-amp’s inverting input must equal the voltage at the non-inverting input. Therefore, the current \(I_R\) through the input resistor is given by:

\[ I_R = \frac{V_{\text{in}}}{R} \tag{1}.\]

We define the current through the capacitor as \(I_C\) and the voltage across the capacitor as \(V_C\). The well-known capacitor current-voltage relation is:

\[ I_C = C \frac{dV_C}{dt} \tag{2}.\]

Since the op-amp has a very high input impedance, the current through the resistor flows entirely to the feedback capacitor, meaning:

\[ I_R = I_C \tag{3}.\]

Substituting the previous equations, we get:

\[ C \frac{dV_C}{dt} = \frac{V_{\text{in}}}{R} \tag{4}.\]

Since \(V_C\) is actually equal to \(-V_{out}\) (one side of the capacitor is connected to 0V and the other to \(V_{out}\) ), we can rewrite the equation as:

\[ – C \frac{dV_{\text{out}}}{dt} = \frac{V_{\text{in}}}{R} \tag{5},\]

\[ \frac{dV_{\text{out}}}{dt} = -\frac{V_{\text{in}}}{RC} \tag{6}.\]

Integrating both sides, we find that the output voltage is the integral of the input voltage, scaled by a constant factor \(-1/{RC}\). This explains why the circuit functions as an integrator.

The problem with the above integrator

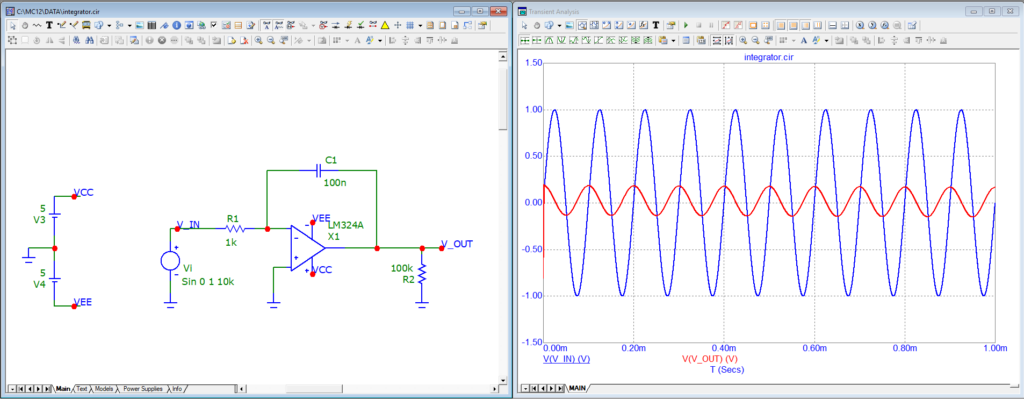

We can verify that this circuit functions as expected by simulating the schematic in Figure 1 using SPICE. The input is a sine wave voltage source with a 1 V amplitude and a 10 kHz frequency. Figure 2 shows the input voltage (blue) and the output voltage (red).

As expected, the output voltage follows a cosine waveform (the integral of a sine wave), with its amplitude attenuated relative to the input:

\[\begin{eqnarray} V_{\text{out}} = -\frac{1}{RC} \int V_{\text{in}} \, dt \\= -\frac{1}{RC} \int \sin(\omega t) \, dt \\= \frac{1}{\omega RC} \cos(\omega t) \end{eqnarray}\tag{7}\]

So, what’s wrong with this circuit? The SPICE simulation results seems to align well with our theoretical equations.

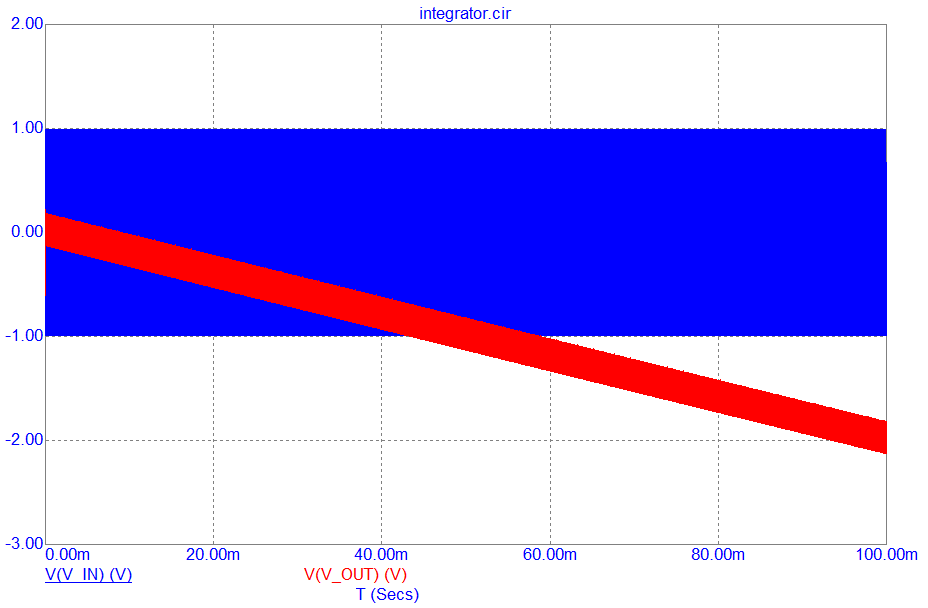

To uncover the problem, we need to take a closer look at the transient response. The previous simulation only observed a short time window—1 ms. But what if we extend the time scale to 100ms? Figure 3 shows the results over this longer period.

We can see that the output voltage is drifting. The cause is the operational amplifier’s input bias current. This is a DC current flowing into or out of the op-amp’s input pins. Where does this current flow? It cannot go through the input resistor because one side of the resistor is at zero volts, meaning the resistor’s current is entirely determined by the input voltage. As a result, the bias current must flow into the capacitor, gradually charging it and shifting the output voltage over time. Since the bias current is typically small, this drift happens slowly. However, over time, it can push the amplifier into saturation.

How to fix the integrator?

A simple solution is to connect a resistor in parallel with the feedback capacitor. This provides a discharge path for the capacitor, limiting the DC error at the output caused by the bias current.

How do we choose the value of this resistor? Since the capacitor has a high impedance at low frequencies, the parallel resistor dominates at those frequencies, effectively turning the circuit into a non-inverting amplifier rather than an integrator. As a result, the circuit will function as an integrator only for frequencies above a certain threshold. The higher the value of the feedback resistor, the lower the frequency at which the circuit behaves as an integrator.

However, a higher feedback resistor also means a greater DC error at the output, and it will take longer for this error to stabilize at its final voltage. Additionally, a larger resistor increases noise. To optimize performance, refer to the op-amp datasheet to check the typical input bias current and ensure the resistor value is appropriate.

Amplifier with an AC-coupled input: similar issue

Consider the circuit in Figure 4: a non-inverting op-amp with an AC-coupled input. This means only the AC component of the input signal is amplified, while the DC component is blocked by the capacitor.

The issue here is similar to the integrator circuit. The input bias current of the op-amp, coming from the positive input pin, will flow into the capacitor, gradually charging it over time. To fix this, add a resistor to ground after the coupling capacitor (on the op amp’s non inverting input pin). This provides a path for the input bias current, preventing unwanted voltage drift.

Ignoring Input Common-Mode Voltage Limitations

Another overlooked issue in many designs with op-amps is neglecting the input common-mode voltage range. Every op-amp has specific limits on the allowable voltage range at its inputs, beyond which the amplifier may exhibit unexpected behavior or fail to function correctly.

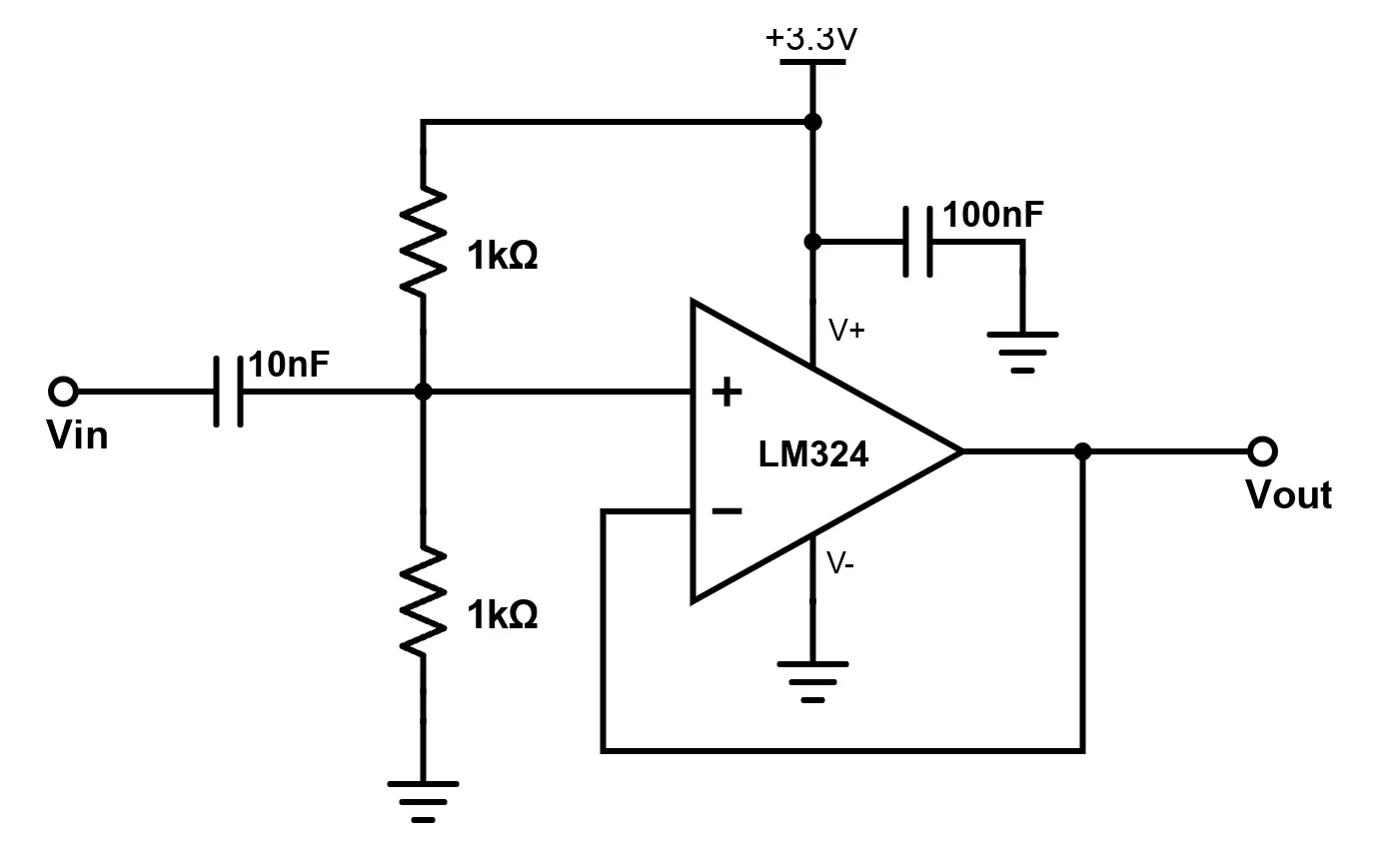

Consider the circuit in Figure 5, which uses an LM324 op-amp powered from a 3.3V single supply. The input is AC-coupled through a capacitor and biased to mid-supply (1.65V) using a voltage divider. The op-amp is configured as a buffer.

The issue here is that the LM324 has a limited input common-mode range—typically from 0V to VCC – 2V, or up to 1.3V in this case. With the input biased at 1.65V, the op-amp is operating outside its valid input range. When this happens, the op-amp may not behave linearly: the output could be distorted, latch up, or show large DC errors. Even if the circuit appears to work, the behavior won’t be guaranteed across temperature or supply variations.

2. Stability and Oscillation Pitfalls in Op-Amp Circuits

Using Too Large a Feedback Resistor

Let’s look at the schematic in Figure 6, which shows a simple non-inverting op-amp with a gain of 2. At first glance, the circuit appears straightforward and functional. However, upon closer inspection, a potential issue could degrade circuit performance or even cause malfunction.

The problem lies in the large resistors used in this circuit. While using large resistors will reduce power dissipation, it is important to take into account their potentially significant noise contribution, as well as the DC errors resulting from the bias and offset currents.

A more critical issue with large feedback resistors is the potential for stability problems, particularly with high-speed amplifiers such as the ADA4817. This arises from a pole formed at the op-amp’s summing junction, created by the interaction between the impedance seen at that node (\(R_F \parallel R_G\)) and the amplifier’s input capacitance. The input capacitance is usually in the range of a few picofarads and can vary depending on the op-amp and PCB layout.

If the resulting pole frequency falls below the loop gain crossover frequency, it will reduce the phase margin and potentially cause oscillations. This issue is particularly relevant for high-speed amplifiers, where the crossover frequency is higher, making it more likely that the added pole will interfere with stability.

To overcome this issue, the feedback resistor should be small enough to ensure that the added pole frequency is well above the crossover frequency. It may be helpful to use the recommended values for the feedback resistor from the op-amp datasheet, or to perform a SPICE simulation such as AC analysis or transient simulation to verify that the selected value is acceptable. If a large feedback resistor must be used to reduce power dissipation, a small capacitor can be added in parallel with it to introduce a zero in the loop gain. This zero compensates for the phase shift introduced by the added pole, improving stability.

Temperature and Bias Effects on Phase Margin

It is possible to evaluate the stability of an op-amp circuit in SPICE. One common method is to simulate the loop gain using the Middlebrook’s method, that involves breaking the feedback loop at a suitable point and inserting an AC voltage source to measure the response. This approach reveals the gain and phase margin of the system.

However, be cautious when interpreting the results: the phase margin can vary with temperature, as the open-loop gain \(A_{OL}\) of the op-amp is temperature dependent. It can also change with different DC operating points. Therefore, it’s recommended to step these parameters in the simulation to make sure the circuit is stable across all operating conditions.

Micro-Cap is a powerful and free SPICE simulator that simplifies this process. It supports both the Middlebrook and Tian methods using a built-in stability probe, and it allows parameter stepping for temperature and other operating conditions directly in the loop gain simulation.

Coupling Between Positive Input and Output

In some cases, a circuit may show good phase margin in simulation but still oscillate in practice. When this happens, the PCB layout is sometimes the culprit. If traces connected to the op-amp’s output and non-inverting input are routed close to each other, capacitive coupling between them can occur. This unintended positive feedback path can degrade phase margin and lead to instability. It’s good practice to review the layout and ensure adequate spacing or shielding between these traces to maintain proper feedback behavior.

Driving Capacitive Loads

Figure 7 shows an example of an op-amp configured as a voltage follower, which serves the purpose of buffering a reference voltage to supply an external reference pin of an ADC. A bypass capacitor of 100 nF is connected to this reference pin as recommended in the ADC datasheet.

The issue with this circuit is that the op-amp’s internal output resistance, in combination with the capacitive load, creates a pole in the loop gain. This pole can decrease the stability of the circuit.

One way to address the issue of op-amp stability with capacitive loading is to add a series resistor between the op-amp and the load capacitor. This resistor isolates the load capacitor from the feedback loop, preventing it from negatively impacting stability. This addition will introduce a zero in the Bode plot of the loop gain, which will cancel out the effect of the pole created by the op-amp’s internal output resistance and the load capacitor.

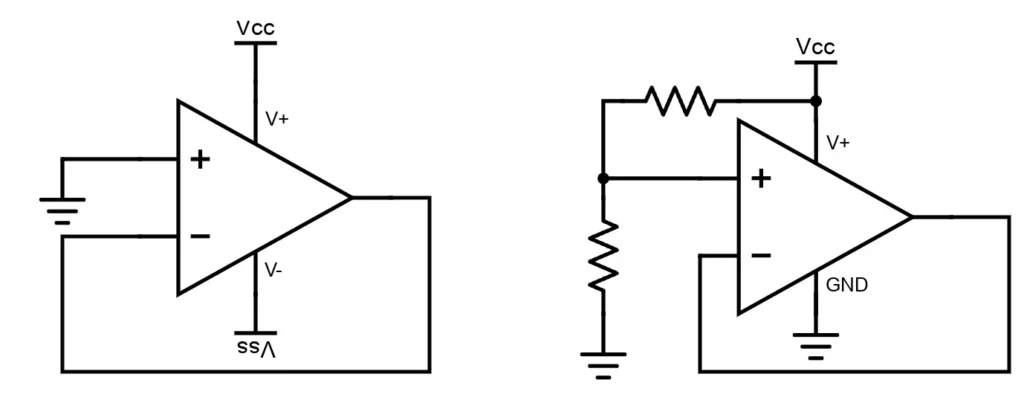

However, adding a series resistor can cause problems when the load draws current, resulting in a voltage drop across the resistor and leading to output voltage variations with changes in current. Another popular method for stabilizing the op-amp without this drawback is by using in-the-loop compensation, as shown in Figure 8:

Finding the optimal values for the compensation resistor and capacitor can be challenging since they depend on the output resistance of the op-amp, which is often not specified in the datasheet, as well as the output capacitance, which can vary. Therefore, it is generally advisable to perform a SPICE simulation and use a trial-and-error method to identify the optimal values. However, it is important to note that the accuracy of the SPICE model for the output resistance may be limited, so it is recommended to verify the results with a real circuit whenever possible.

3. Practical Design Oversights for Reliable Op-Amp Circuits

Handling Unused Op-Amps in Multi-Op-Amp Packages

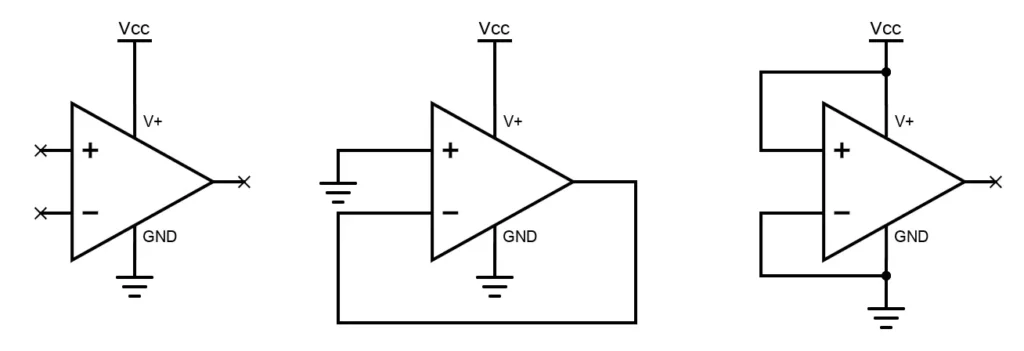

Sometimes we use an IC package that contains multiple op-amps, but we don’t always use all of them. A common mistake is to leave the unused op-amp input pins floating or connecting them to ground. This can lead to unexpected behavior, such as saturating the output at an unknown state, leading to increased current consumption, or noise pickup that couples into the used amplifiers in the package or the supply rail.

Another mistake is connecting a single supply unused op-amp in a voltage follower configuration with the non-inverting input connected to ground. This keeps the amplifier in saturation and increases current consumption. Connecting one input to the lower rail and the other to the high rail is also not recommended, as it will also keep the amplifier in saturation, and additionally it may exceed the specified absolute maximum differential voltage, leading to damage.

The correct ways to connect an unused op-amp are shown in Figure 10. The op-amps are connected in the voltage follower configuration, with their non-inverting input connected to some voltage that is within the specified input common mode voltage range.

Designing for Low-Current Measurements

Designing circuits for low-current measurements requires careful attention to minimize errors and ensure accuracy. Texas Instruments’ Application Note 241, “Working with High Impedance Op Amps,” offers valuable insights into this topic.

The note discusses advancements in op-amp technology that have significantly reduced input bias currents, enhancing performance in high-impedance applications. It addresses challenges such as printed circuit board (PCB) leakage, cable leakage, noise generation, semiconductor switch leakages, and limitations of large-value resistors and capacitors. Practical solutions are provided, including the use of guarding techniques to reduce PCB leakage, bootstrapping to mitigate cable capacitance effects, and selecting appropriate components to minimize noise and leakage currents.

Using an Op-Amp as a Comparator

Sometimes it is tempting to use an op-amp instead of a comparator. For example, when we already have an IC package with multiple op-amps, and one of them is not used, we might use it as a comparator. Similar to a comparator, an op-amp operating without feedback will compare its two input voltages and produce an output voltage saturated at one of the rails, indicating which of the two input signals is larger or smaller.

However, using an op-amp as a comparator is a bad idea in many cases. An op-amp, unlike a comparator, is not optimized for operation in an open loop with a large differential input voltage and a saturated output. Therefore, its performance will be inferior to a comparator under these conditions. It will take a long time for the op-amp to recover from saturation when its inputs are overdriven, and this time is usually not specified in the datasheet, nor is it included in the op-amp’s SPICE model.

In addition, in some op-amps, the input differential voltage range is limited. If a higher differential voltage is applied, the internal protection diodes may start to conduct, which can damage the op-amp. It is also important not to operate the op-amp outside the specified input common mode voltage range, as the performance will be undefined and some op-amps may be susceptible to output phase reversal phenomenon which is highly undesirable in comparator applications.

—

Have you run into other op-amp design mistakes that caught you by surprise? Share your experiences or tips in the comments. And stay tuned for the next article in this series, where we’ll dive into more common (and sometimes overlooked) electronics design mistakes.

Share this on: